## COMPUTER-AIDED PARALLELIZATION OF APPLICATIONS

## THÈSE Nº 2431 (2001)

PRÉSENTÉE AU DÉPARTEMENT D'INFORMATIQUE

## ÉCOLE POLYTECHNIQUE FÉDÉRALE DE LAUSANNE

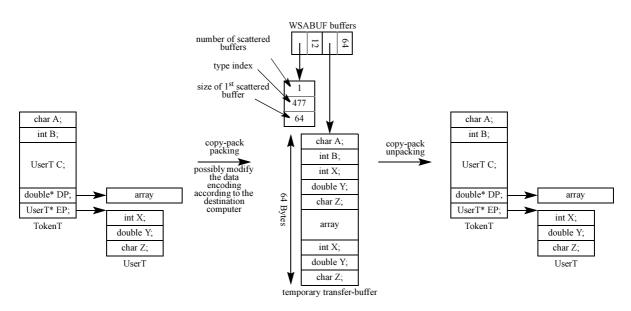

POUR L'OBTENTION DU GRADE DE DOCTEUR ÈS SCIENCES TECHNIQUES

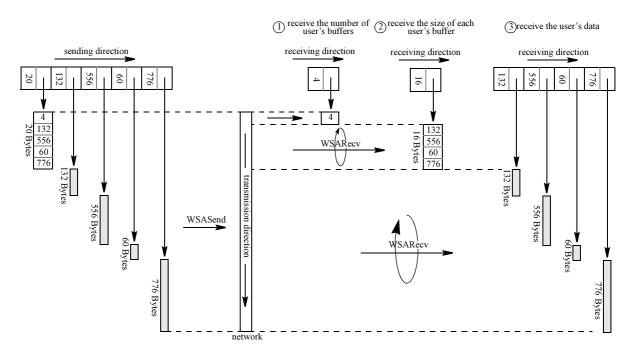

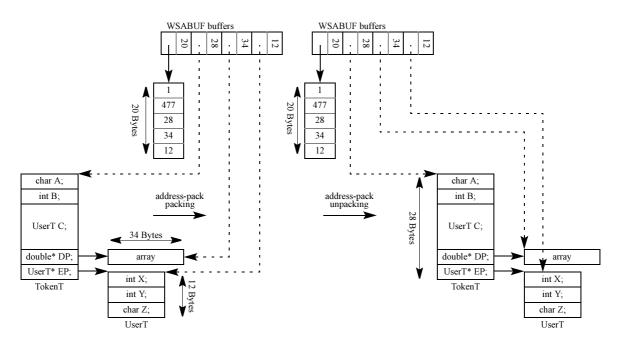

PAR

### Marc MAZZARIOL

Ingénieur informaticien diplômé EPF originaire de Genève

Jury de thèse:

Prof. R. D. Hersch, directeur de thèse Prof. R. Guerraoui, rapporteur Dr B. Gennart, rapporteur Dr M. Snir, rapporteur

> Lausanne, EPFL 2001

A mon père

"No Brain, No Headache"

Ann O'Nym

# Acknowledgements

First and foremost, I am especially grateful to my research director, Professor Roger David Hersch, who offered me a challenging and interesting research area, who gave me guidance and support throughout this research, and spent hours reading and commenting on earlier drafts of this dissertation. His continuous support and guidance were an incomparable stimulation and helped me to focus my attention on the essentials to reach my objectives.

I am particularly indebted to Dr. Benoît Gennart and Dr. Vincent Messerli for their technical expertise and for the enlightening discussions we had, which helped me clarify my ideas and led me to new ideas. Dr. Benoît Gennart and Dr. Vincent Messerli are the main authors of the CAP/PS<sup>2</sup> parallelization framework. The present thesis wouldn't have been possible without their own work.

I would like to thank the members of the Peripheral System Laboratory, among them Oscar Figueiredo, Jean-Christophe Bessaud, Joaquín Táraga, Emin Gabrielyan, Sebastian Gerlach, Olivier Courtois, Itzhak Amidror, Yvette Fishman, Fabienne Allaire, and all the LSP staff for making the LSP such a nice place to work in. They made this research enjoyable on a day-to-day basis providing encouragement and motivation.

I am also thankful to my previous teachers and all the people who helped me to develop my curiosity, and who gave me a taste for research. In particular, I would like the thank Olivier Fischer, Xavier Montet and Laurent Herrmann.

I am especially grateful to all my family, my friends, and all those I met during my sport activities. All of them supported me and helped along the years, sometimes without knowing how much!

Finally I thank the Swiss National Fund and the EPFL for funding this research.

# **Summary**

Within the scope of this thesis, we are interested in running high-performance parallel applications on clusters of commodity components, i.e. PCs or workstations. Creating parallel applications remains a difficult task. Moreover, creating efficient pipelined parallel schedules where communication, computation and I/O are carried out simultaneously is a real challenge.

We use the Computer-Aided Parallelization (CAP) framework developed at EPFL in order to facilitate the design and development of pipelined parallel applications. The CAP based parallelization approach differs from other parallelization approaches by freeing the programmer from low-level issues such as thread management, protocol management and synchronization. The programmer can concentrate his efforts on building efficient parallel schedules. Application programmers express separately the serial program parts and the parallel behavior of the program at a high level of abstraction, i.e. as a parallel schedule. The parallel schedule determines the flow of data and parameters between operations running on the same or on different processors. CAP offers asynchronous processing capabilities allowing to carry out simultaneously I/O operations, communications and computations.

In this thesis, we show how parallel applications from various domains can be developed by taking advantage of CAP: parallel linear algebra algorithms such as matrix multiplication and LU decomposition, parallel image filtering, parallel cellular automata and parallel discrete optimization algorithm such as Branch and Bound. We are also interested in the parallelization of industrial applications, such as the *Radiocontrol* application aiming at computing in parallel the listening quotes of radio stations.

The contributions of this thesis are (1) to validate the CAP C++ language extension by demonstrating its capability of synthesizing parallel programs, and (2) to show that the CAP based parallelization approach yields efficient parallel programs in different application fields.

The reader is introduced to the CAP philosophy and to the formulation of parallel schedules. We discuss flow-control and load balancing issues and propose appropriate CAP constructs. In several parallel applications, we demonstrate the compositionality of CAP and its benefits. In order to demonstrate the performance offered by CAP, we create for most applications a performance model and verify it by experimental measurements. Finally, we describe the perspectives and give ideas for pursuing this research.

# Résumé

Dans le cadre de cette thèse, nous avons étudié la réalisation d'applications parallèles sur un ensemble d'ordinateurs communément disponibles sur le marché (PCs ou stations de travail). La création d'applications parallèles reste à ce jour une tâche difficile et fastidieuse. En particulier, la mise en oeuvre d'ordonnancements parallèles performants où les communications, le calcul et les entrées/sorties s'exécutent simultanément est un défi.

L'environnement de parallélisation CAP développé à l'EPFL facilite la réalisation d'applications parallèles complexes. La méthodologie de parallélisation CAP se distingue des autres outils de parallélisation en libérant le programmeur de l'implémentation de tâches de bas niveau tels que la gestion des threads, la gestion de protocol et la synchronisation. Le programmeur peut se concentrer spécifiquement sur la création d'ordonnancements parallèles complexes et efficaces. Le programmeur exprime l'ordonnancement parallèle des tâches indépendamment de la partie sérielle de l'application. Afin d'offrir un maximum de souplesse, CAP permet d'exprimer les ordonnancements parallèles avec un niveau d'abstraction suffisant. De ces ordonnancements sont déduis les dépendances et flux de données entre les tâches s'exécutant sur les différents processeurs. Afin de permettre la réalisation de schéma d'exécution où les communications, le calcul et les entrées/sorties s'effectuent simultanément, CAP offre la possibilité d'exécuter des opérations de façon asynchrone.

Au travers de cette thèse, nous montrons comment des applications parallèles de différents domaines peuvent bénéficier de la méthodologie de parallélisation CAP. En particulier nous étudions le développement d'algorithmes parallèles d'algèbre linéaire (multiplication matricielle, décomposition LU), de filtrage d'image, d'automate cellulaire et d'optimisation combinatoire (Branch and Bound). Nous présentons aussi la parallélisation d'une application industrielle (*Radiocontrol*) qui a pour objectif d'établir l'audimat des stations radio.

La contribution de cette thèse est (1) de valider le langage de parallélisation CAP (extension du C++) en démontrant sa capacité à formuler de façon synthétique des programmes parallèles, et (2) de montrer que la méthodologie de parallélisation CAP permet de paralléliser efficacement des applications de différents domaines.

Au travers de cette thèse, le lecteur est d'abord initié à la philosophie CAP et à la formulation d'ordonnancements parallèles. Nous étudions les problèmes de contrôle de flux de données et d'équilibrage de charge de travail entre processeurs et proposons des constructions adéquates en CAP. Au travers de plusieurs applications, nous montrons l'aspect compositionnel de CAP et ses avantages. Afin de démontrer les performances de CAP, pour la plupart des applications, nous créons un modèle de performances et le vérifions expérimentalement. Nous concluons, en indiquant les perspectives et les suites à donner à cette recherche.

# Table of Contents

| Acknowledgements<br>Summary                                                                                                                                                                 | vii  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                                                                             | ix   |

| Résumé                                                                                                                                                                                      | xi   |

| Table of Contents                                                                                                                                                                           | xiii |

| 1 Introduction and Related Work                                                                                                                                                             |      |

| <ul> <li>2 Basic notions and parallelization fundamentals</li> <li>2.1. Performance Measurements</li> <li>2.1.1. Speedup</li> <li>2.1.2. Efficiency</li> <li>2.1.3. Amdahl's law</li> </ul> |      |

| 2.2. Granularity                                                                                                                                                                            |      |

| 2.3. Parallel processing and pipelining                                                                                                                                                     |      |

| 2.4. Master-slave or distributed system                                                                                                                                                     |      |

| 2.5. Load balancing                                                                                                                                                                         |      |

| 2.6. Asynchronous behaviour                                                                                                                                                                 |      |

| 2.7. Flexibility                                                                                                                                                                            |      |

| <ul><li>2.8. Reliability and error handling</li><li>2.9. Summary</li></ul>                                                                                                                  |      |

| 3 The CAP Computer-Aided Parallelization Tool                                                                                                                                               |      |

| 3.1. Introduction                                                                                                                                                                           |      |

| 3.2. Tokens                                                                                                                                                                                 |      |

| 3.3. Process hierarchy                                                                                                                                                                      |      |

| 3.3.1. Configuration file                                                                                                                                                                   |      |

| 3.4.1. Leaf operations<br>3.4.2. Parallel operations                                                                                                                                        |      |

| <ul><li>3.5. Parallel CAP constructs</li><li>3.5.1. The <i>pipeline</i> CAP construct</li><li>3.5.2. The <i>indexed parallel</i> CAP construct</li></ul>                                    |      |

| 3.6. Summary                                                                                                                                                                                |      |

| 4 CAP flow-control and load balancing issues                                                                                                                                                |      |

| 4.1. Introduction                                                                                                                                                                           |      |

| 4.2. CAP flow-control issues                                                                                                                                                                |      |

| 4.3. Issues of load balancing in a pipelined parallel execution                                                                                                                             |      |

| 4.4. Summary                                                                                                                                                                                |      |

| 5 CAP Message passing and Serialization                      |     |

|--------------------------------------------------------------|-----|

| 5.1. The CAP token-oriented Message-Passing System (MPS)     |     |

| 5.2. Serialization of CAP tokens                             | 56  |

| 5.3. Automatic serialization of CAP tokens                   | 60  |

| 5.4. Integration                                             |     |

| 5.5. Summary                                                 | 63  |

| 6 Parallel linear algebra algorithm                          |     |

| 6.1. Introduction                                            |     |

| 6.2. Matrix Multiplication                                   |     |

| 6.2.1. Notations and problem formulation                     |     |

| 6.2.2. Dynamic parallel algorithm                            |     |

| 6.2.3. Dynamic parallel algorithm: theoretical analysis      |     |

| 6.2.4. CAP specification of the matrix multiplication        |     |

| 6.3. LU factorization                                        | 69  |

| 6.3.1. Problem description                                   |     |

| 6.3.2. Parallelization                                       |     |

| 6.4. Performance measurements                                | 74  |

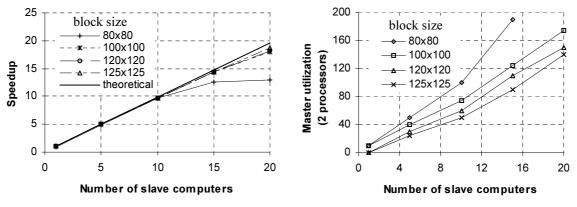

| 6.4.1. Dynamic matrix multiplication                         |     |

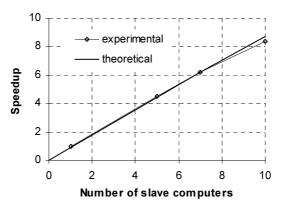

| 6.4.2. LU factorization                                      |     |

| 6.4.3. Analysis of results                                   |     |

| 6.5. Summary                                                 | 77  |

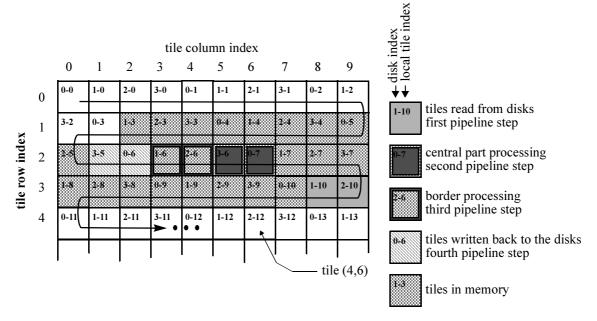

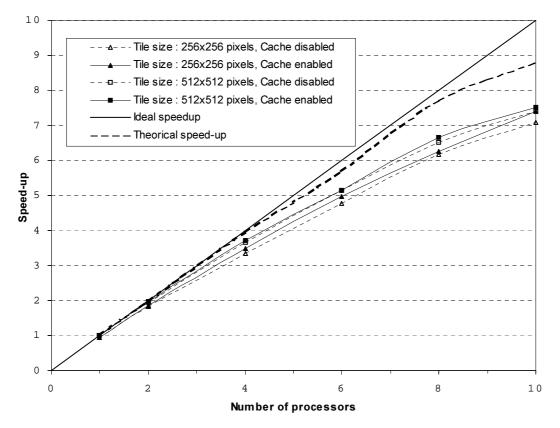

| 7 Parallel Imaging                                           | 79  |

| 7.1. Introduction                                            | 79  |

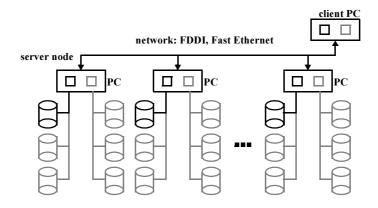

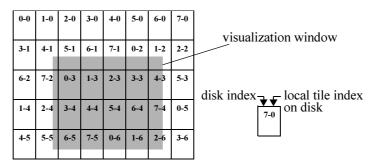

| 7.2. System support for managing large images                | 80  |

| 7.2.1. Hardware architecture                                 |     |

| 7.2.2. Software architecture                                 |     |

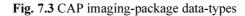

| 7.3. The parallel process-and-gather operation               |     |

| 7.3.1. Problem description                                   |     |

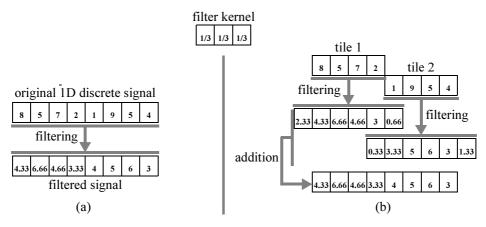

| 7.3.2. Modelled single-PC execution schedule                 |     |

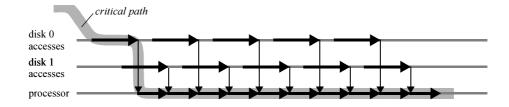

| 7.3.3. Modelled multiple-PC execution schedule               |     |

| 7.3.4. Theoretical performance analysis                      |     |

| 7.3.5. CAP specification of the process-and-gather operation | 0.6 |

| 7.4. The exchange-process-and-store operation                |     |

| 7.4.1. Problem description                                   |     |

| 7.4.2. Theoretical performance analysis                      |     |

| 7.4.3. CAP specification<br>7.5. Performance results         | 02  |

| 7.6. Summary                                                 |     |

| -                                                            |     |

| 8 Parallel Cellular Automata                                 |     |

| 8.1. Introduction                                            |     |

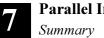

| 8.2. Image skeletonization algorithm                         |     |

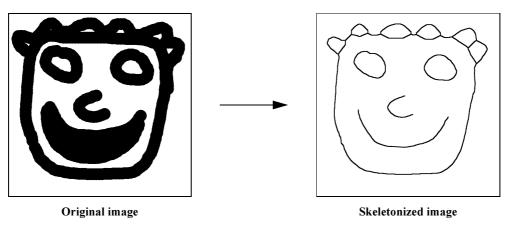

| 8.2.1. Improvement of the image skeletonization algorithm    |     |

| 8.3. Parallel skeletonization with static load distribution  |     |

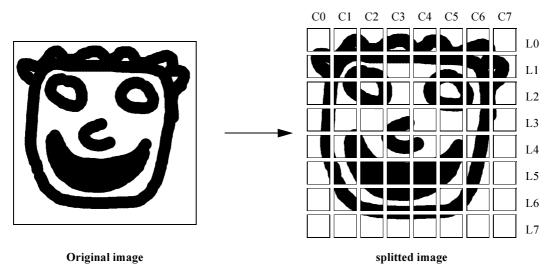

| 8.4. Dynamic load balanced parallel scheme                   |     |

| 8.5. CAP specification                                       |     |

| 8.6. Performance measurement                              | . 106 |

|-----------------------------------------------------------|-------|

| 8.7. Summary                                              | . 109 |

| 9 Parallel Computation of Radio Listening Rates           | . 111 |

| 9.1. Introduction                                         | . 111 |

| 9.2. The matching problem                                 | . 112 |

| 9.2.1. Storage                                            |       |

| 9.2.2. Serial correlation algorithm                       |       |

| 9.2.3. Serial performance analysis/measurements           |       |

| 9.3. Parallelization                                      | . 116 |

| 9.3.1. The Computer-Aided Parallelization (CAP) framework |       |

| 9.3.2. Parallel correlation algorithm                     |       |

| 9.3.3. CAP program specification                          |       |

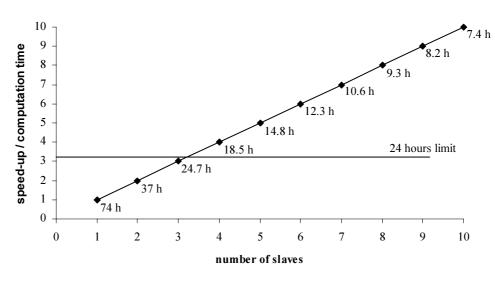

| 9.3.4. Parallel performance analysis/measurements         |       |

| 9.4. Graceful degradation in case of failure              | . 121 |

| 9.5. Summary                                              | . 122 |

| 10 Discrete Optimization Problems                         | . 125 |

| 10.1. Parallelization of hard nonnumeric problems         | . 125 |

| 10.2. Discrete optimization problems                      | . 125 |

| 10.3. Heuristics                                          | . 127 |

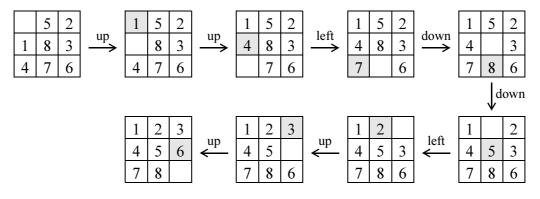

| 10.4. Sequential search algorithms                        | . 128 |

| 10.4.1. Depth-first search                                |       |

| 10.4.2. Breath-first search                               |       |

| 10.4.3. Best-first search                                 |       |

| 10.4.4. Branch and bound                                  |       |

| 10.4.5. Generic sequential search                         |       |

| 10.5. Parallel search                                     | . 133 |

| 10.6. Travelling Salesman Problem: A didactical solution  | . 134 |

| 10.6.1. Process hierarchy                                 |       |

| 10.6.2. Sequential part of the algorithm                  |       |

| 10.6.3. Parallel part of the algorithm                    |       |

| 10.7. Summary                                             | . 141 |

| 11 Conclusion                                             | . 143 |

| Bibliography                                              | . 145 |

| Biography                                                 | 153   |

# 1

## **Introduction and Related Work**

What is parallel computing? Let us answer this question by drawing an analogy to a real-world scenario. Consider the problem of delivering letters in a village. If the post office hires only a single postman, he cannot accomplish the task faster than a certain rate. This process can be speeded up by employing more than one postman. One simple way to assign the task to the postmen is to divide the letters equally among them. Each postman starts then the delivery of his set of letters. However, this division of work may not be the most efficient way to accomplish the task, since each postman must walk all over the whole village. An alternate way to divide the work is to assign disjoint regions of the village to each postman. As before, each postman is assigned an equal number of letters arbitrarily. If a postman finds a letter that belongs to the region of the village assigned to him, he delivers that letter. Otherwise, he passes it on to the postman responsible for the region of the village it belongs to. The second approach requires less effort from individual postmen.

The preceding example shows how a task can be accomplished faster by dividing it into a set of sub-tasks assigned to multiple postmen. Postmen cooperate, pass the letters to each other when necessary, and accomplish the task in unison. Parallel processing works on precisely the same principles. Dividing a task among postmen by assigning them a set of letters is an instance of *task partitioning*. Passing letters to each other is an example of *communication* between sub-tasks. Task partitioning and communication are the main issues of parallel processing. *Synchronization* between tasks is also a critical point, but it can be considered as part of the communication.

Problems are parallelizable to different degrees. For some problems, assigning portions to other processors might be more time-consuming than performing the tasks locally. Other problems can be carried out only serially. For example, consider the task of hammering a nail. Although one person can hammer a nail in a certain amount of time, employing more people does not reduce this time. Because it is impossible to partition this task, it is poorly suited to parallel processing. All problems are not equally amenable to parallel processing and moreover, a problem may have different parallel formulations, which result in varying benefits [Kumar94].

Parallelism appears in various domains as a natural way to improve the performance. If you are cooking in your kitchen and you want to accelerate this process, you will ask someone to help you. By communicating together you will be able to cooperate efficiently and reduce cooking time. More generally, the organization of our society could be considered as a huge parallel process with several (hierarchical) communication layers. From the biological point of view, our brain or any multi cellular organism could be seen as a parallel system. The cells collaborate together to coordinate their work. The multi cellular system seems well organized. This collaboration is ensured by several biological mechanisms (hormones, neurotransmitters, etc.).

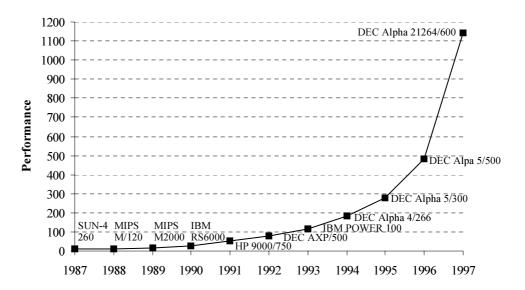

Figure 1.1 plots the top performance per year of workstations between 1987 and 1997 [Patterson97]. The performance of a computer depends directly on the time required to perform a basic operation and the number of these basic operations that can be performed concurrently. The time to perform a basic operation is ultimately limited by the *clock cycle* of the processor, that is, the time required to perform the most primitive operation. However, clock cycle times will not decrease indefinitely due to physical limitations. To circumvent these limitations, the designer may attempt to utilize internal concurrency in a chip, for example, by implementing pipelining, or by operating simultaneously on all 64 bits of two numbers that are to be multiplied. However, a fundamental result in Very Large Scale Integration (VLSI) complexity theory says that this strategy is expensive. Building individual components operating faster is difficult. It may be cheaper and more efficient to connect together slower components [Foster94]. Another important trend that is changing the face of computing is the enormous increase in the capabilities of networks that connect computers. Not long ago, high-speed networks ran at 1.5 Mbits/s; currently 100 Mbits/s and soon 1Gbits/s are commonplace. Considering the evolution of computer technologies, parallel computing appears as a natural way to circumvent the future limitation of computing power.

Fig. 1.1 Performance increase of workstations, 1987-1997. Here performance is given as approximately the number of times faster than the VAX-11/780, which was a commonly used yardstick. The rate of performance improvement is about 1.54 per year, or doubling every 1.6 years. These performance numbers are from the integer SPEC92 benchmarks (SPECbase\_int92) except the two later machines based on the SPECin95base and multiplied by a factor to estimate SPECbase92 performance.

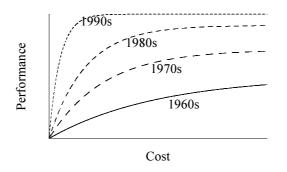

Figure 1.2 represents typical cost-performance curves of serial computers over the last few decades. Beyond a certain point, each curve starts to saturate, and even small gains in performance come at an exorbitant increase in cost. Furthermore, this transition point has become sharper with the passage of time. By connecting only a few commodity computers together to form a parallel computer, it is possible to obtain raw computing power comparable or even

higher than the fastest serial computers. Typically, the cost of such a parallel computer is considerably lower. From the economical point of view, parallel computing appears also as a natural solution to improve performances with reasonable costs.

Fig. 1.2 Cost versus performance curve and its evolution over the decades

The previous considerations show us that the idea of parallel processing is a reality imposing itself naturally in the computer sciences. The concept of a computing system consisting of multiple processors working in parallel on different problems or different parts of the same problem is not new. Discussions of parallel computing machines are found in the literature at least as far back as the 1920s [Crichlow97][Denning86]. Throughout the years, there has been a continuing research effort to understand parallel computation. In the 1980s, technical developments (VLSI, large memories, parallel and pipeline ALUs, etc.) reduced the costs of producing computer components while at the same time increasing performance in terms of processing time, quantity of data processed and reliability [DeCegama89]. During the 1980s, the appearance of personal computers enhanced the productivity of individuals, and in turn, the productivity of companies. Since large companies are made up of individuals, the productivity improvement of individuals using stand-alone computers was too compelling to ignore. PCs soon became pervasive [Lewis92]. The 1990 decade is to parallel computing what the 1980 decade was to personal computing. Since the early 1990 there has been an increasing trend to move away from expensive and specialized proprietary parallel supercomputers towards networks of workstations or PCs. Among the driving forces that have enabled this transition has been the rapid improvement in the availability of commodity high performance components for workstations and networks. These technologies are making networks of computers an appealing vehicle for parallel processing, and this is consequently leading to low-cost *commodity supercomputer*.

Let us focus on the effervescence of workstation networks. Why did they become so popular? What are their main advantages compared to a specialized proprietary parallel supercomputer? We already saw that workstation clusters are cheaper and readily available. Their exploitation and maintenance are also less expensive. Workstation clusters are easy to integrate into existing networks. In terms of performance, individual workstations are becoming increasingly powerful. The communication bandwidth between workstations is increasing and latency is decreasing as new networking technologies and protocols are implemented in a LAN (Fast Ethernet, Gigabit Ethernet, Myrinet, FDDI). From an other point of view, the development tools for workstations are more mature compared to proprietary solutions for parallel computers, mainly due to the nonstandard nature of parallel computers [Buyya99]. Cluster of workstations benefit from the explosion of Internet and the necessity for small businesses to acquire reliable and efficient parallel WWW servers. For many customers and applications, 100 processors provide sufficient computing power. In 1997, most multiprocessor systems were in the range of 8 to 16 processors, with the number moving up slowly. Cluster based solutions correspond to current market necessities.

Traditionally, in science and industry, a workstation referred to a UNIX platform. There has been, however, a rapid convergence in processor performance and kernel-level functionality of UNIX workstations and PC-based machines in the last years. This can be attributed to the introduction of high performance Pentium-based machines and the apparition of operating systems such as Linux, Windows NT and Windows 2000. This convergence has led to an increased level of interest in utilizing PC-based systems as a cost-effective computational resource for parallel computing. This factor coupled with the comparatively low cost of PCs and their widespread availability in both academia and industry has helped to initiate a number of software projects whose primary aim is to harness these resources in some collaborative way [Buyya99].

The next generation of parallel computers is based on clusters of PCs. All the hardware components (processor, network, storage disk) are commodity components. Developing efficient parallel applications on non-dedicated hardware becomes a main research topic. The emergence of distributed memory systems connected through standard high latency networks has a major impact on the conception of parallel applications. Explicit parallelization programming models seem to offer better performance than implicit ones. Implicit parallelization models are based on compiler parallelization which suffers from the difficulties for the compiler to determine the most suitable way to automatically convert sequential programs into efficient parallel ones (compilers for several parallel architectures and languages exists, e.g. Fortran [Koelbel94][Wolfe82]). The difficulties are due to the fact that the compiler must analyze and understand the dependencies in different parts of the sequential code in order to ensure an efficient mapping onto a parallel computer. The explicit parallel programming model requires a parallel algorithm which explicitly specifies how the processors cooperate in order to solve a specific problem. The compiler's task becomes straightforward. However, the programmer's task is quite difficult. Explicit parallelization programming models on distributed memory systems are mostly based on message passing models [Crichlow97], e.g. Concurrent Pascal [Hansen75], Occam [Inmos85][Galletly96]. In order to offer better code portability, architecture independent message passing libraries such as MPI [MPI94] and PVM [Sunderam90] have been developed. However, programs are usually still difficult to understand, debug, and maintain. The direction in language development has been towards making a program more and more a collection of classes, with their private lives separated from their public lives, i.e. object oriented programming [Ghezzi82][Ghezzi85]. The history of programming languages shows a discernible trend towards higher levels of abstraction [Watt90]. We believe that this point is essential in parallel programming languages. This philosophy is shared with many other researchers [Beguelin92][Hatcher91][Shu91]. In order to provide a higher-level language interface simplifying parallel application development new language extensions such as like CAP or MENTAT [Grimshaw93b] have appeared.

The CAP Computer-Aided Parallelization tool has been created by Dr. Benoît Gennart at the Peripheral System Laboratory (LSP) of EPFL. The application programmers express separately the serial program parts and the parallel behavior of the program at a high level of abstraction. This high-level parallel CAP program description specifies a macro-dataflow, i.e. a flow of data and parameters between operations running on the same or on different processors. CAP features also asynchronous processing allowing to handle efficiently I/O bound parallel applications. The CAP framework and its associated parallel file striping services (PS<sup>2</sup>) are described in [Gennart98a][Messerli99a].

Within the scope of this thesis we are interested in running high-performance parallel applications on clusters of commodity components, i.e. PCs or workstations. By cluster, we mean a collection from 2 to 50 computers. We are not interested in massively parallel architectures but in small/medium ones. This kind of architectures corresponds to current market necessities. Parallel computing appears from many point of views (computing power, costs, scalability, simplicity, flexibility) as offering potentially efficient solutions. Nevertheless, exploiting this potential remains a difficult task. Building efficient parallel schedules is an art. In this thesis, we present the development of several parallel applications from different domains. We use the CAP framework in order to facilitate the design and development of these parallel applications. The CAP based parallelization approach differs from other parallel frameworks in that it lets the programmer concentrate his efforts on building efficient parallel schedules. However, the fundamental concepts could be transposed to any other parallel language. Within this thesis, we describe our methodology which leads to the development of efficient parallel solutions.

Chapter 2 introduces the reader to the basic parallel notions. We introduce the notion of speedup and analyze theoretical limitations. We present several techniques such as pipelining. load balancing, and asynchronous execution behavior, allowing to improve parallel algorithms. We treat also the problem of reliability of parallel applications. All these considerations are the fundamentals of the CAP based parallelization approach. This chapter presents the underlying philosophy, concepts, and motivations of the CAP framework, without entering into the syntactical details of the CAP language extension. Chapter 3, instead, presents the CAP language from the syntactical point of view. We present the major parallel constructions of CAP. We present how parallel-pipeline execution schemes can be expressed within the CAP language. Chapter 4 presents advanced CAP features such as load balancing and resource handling in order to implement efficient parallel programs. Chapter 5 is dedicated to the CAP runtime system and in particular to the CAP Message-Passing System (MPS) and the serialization tool. Chapters 3 to 5 should allow the reader to familiarize itself with the CAP framework and understand the CAP programs presented in the following chapters. Chapter 6 is dedicated to parallelization of linear algebra algorithms. In particular, we focus on the parallelization of the well-known BLAS routines [Anderson95]. In Chapter 7, we solve the problem of parallel filtering of large images. Chapter 8 treats the parallelization of cellular automata and the inherent dynamic load balancing problem. In Chapter 9, we present the development of the *Radiocontrol* industrial application.

This application has been developed under industrial constraints; in particular we treat the problem of reliability. The last chapter is a didactical chapter dedicated to the parallelization of discrete optimization problems.

This thesis is dedicated to the application of the CAP parallelization methodology, which is based on the formulation of parallel schedules. The contribution of this thesis is (1) to validate the CAP language extension by demonstrating its capability of handling parallel programs and simplifying their development, and (2) to validate the CAP based parallelization approach by presenting efficient parallel programs. Beyond the research work of this thesis, a large collaborative effort with industrial partners has been performed. Currently the CAP framework and its underlying parallelization techniques are used by several companies.

# 2

### **Basic notions and parallelization fundamentals**

This chapter presents important issues in parallel processing. We focus our interest on the central problem of achieving good performance in terms of scalability. Amdahl's law is discussed in order to explain the inherent difficulties of parallel processing. Then we introduce several concepts such as pipelining, load balancing or asynchronous execution behavior, which need to be considered in order to implement efficient parallel programs. These concepts are the fundamentals of the CAP language extension. Without presenting the syntax of CAP, we explain the fundamental motivation of building a parallel framework such as CAP. This chapter introduces the art of building parallel schedules.

#### 2.1. Performance Measurements

In parallel programming, as in other engineering disciplines, the goal of the design process is to optimize a solution in terms of execution time, memory requirements, implementation costs, maintenance costs, etc. Such a design optimization involves tradeoffs between simplicity, performance, portability, scalability, and other factors. The relative importance of these diverse factors will vary according to the nature of the problem at hand.

In order to evaluate the performance of an algorithm, we need to provide several metrics. A sequential algorithm is usually evaluated in terms of its execution time, expressed as a function of the size of its input. To evaluate parallel algorithms, we must consider, in addition to the execution time, their scalability, the mechanisms by which data is generated, stored, transmitted over networks, moved to and from disks, and passed between different stages of computations. Diverse metrics, such as execution time, parallel efficiency, throughput and latency (network or I/O), should be considered to evaluate the performance of parallel algorithms. Once the costs of these metrics have been determined for a specific parallel algorithm, a *performance model* can be established. These models can be used to compare the efficiency of different algorithms, to evaluate scalability, and to identify *bottlenecks* and other inefficiencies. Performance models can also be used to guide implementation efforts by showing where optimization is needed.

In this section, we introduce some metrics that are commonly used to measure the performance of parallel systems.

#### 2.1.1. Speedup

When evaluating a parallel system, we are often interested in knowing how much performance gain is achieved by parallelizing a given application over a sequential implementation. Speedup is a measure that captures the relative benefit of solving a problem in parallel. It is defined as the ratio of the time taken to solve a problem on a single processor to the time required to solve the same problem on a parallel computer with p identical processors. Let us denote  $t_s$  the

sequential execution time, and by  $t_p$  the parallel execution time. We define speedup by the function S(p):

$$S(p) = \frac{t_s}{t_p} \tag{2-1}$$

For a given problem, several sequential algorithms may be available, but all of these may not be equally suitable for parallelization. When a serial computer is used, it is natural to use the sequential algorithm that solves the problem in the least amount of time. Given a parallel algorithm, it is fair to judge its performance with respect to the fastest sequential algorithm for solving the same problem on a single processor<sup>1</sup>. As a consequence, the sequential time  $t_s$  used in the speedup definition of equation (2-1) has to be the time taken by the best known serial algorithm.

When looking at the speedup we are in general interested in the evolution of S(p) according to increasing values of p, rather than in a single value of the speedup function. This informs us about the *scalability* of the parallel algorithm. Several terminologies are used to characterize the speedup function. The speedup is *ideal* if S(p) = p. The speedup is said *superlinear* (resp. *sublinear*) if, for some p, S(p) > p (resp. S(p) < p). We speak about *linear* speedup when  $S(p) = \alpha p$  (for some  $\alpha$ ), i.e. when the parallel program is scalable. In general, all those characterizations are valid on a specific parallel architecture and within a given range of p. Both the parallel architecture and the considered range of p values must be clearly specified when speaking about speedups.

The parallel algorithm spends some execution time for communication and synchronization purposes. This implies that theoretically, the speedup can never exceed the number of processors p (a formal proof is given in [Cosnard95]). In practice, superlinear speedups (an example is described in Chapter 10) are observed. This is usually due either to a nonoptimal sequential algorithm or to hardware characteristics that put the sequential algorithm at a disadvantage. For example, the data for a problem might be too large to fit into the main memory of a single processor, thereby degrading its performance due to the use of secondary storage. But when partitioned among several processors, the individual data-partitions would be small enough to fit into their respective processor's main memories [Kumar94].

A general way to analyze parallel programs is to establish the speedup function and to consider the differences with the ideal speedup. In a second step, these differences should be explained by an appropriate performance model describing the parallel algorithm. The role of the performance model is to identify the bottlenecks, algorithm inefficiencies, and/or parallel architecture limitations. Finally, these explanations could be used to improve the parallel algorithm.

<sup>&</sup>lt;sup>1</sup> If the sequential algorithm used for the comparison is not the best serial algorithm but the same as the parallel algorithm running on one computer, then we measure the *relative speedup* as opposed to *true speedup* [Patterson97].

#### 2.1.2. Efficiency

An ideal parallel system containing p processors can deliver a speedup equal to p. In practice, ideal behavior is not achieved because while executing a parallel algorithm, the processors cannot devote 100% of their time to the computations of the algorithm. The *efficiency* measures the fraction of time in which a processor is usefully employed. The efficiency function E(p) is defined as the ratio of the speedup to the number of processors.

$$E(p) = \frac{S(p)}{p} \tag{2-2}$$

Ideally the efficiency should be equal to one. In practice, the efficiency is between zero and one, depending on the degree of effectiveness with which the processors are utilized.

#### 2.1.3. Amdahl's law

Various authors attempted to specify the speedup limits. In 1967, Gene Amdahl asserts that the inherent fraction of a program's execution time that must be carried out serially dominates the overall execution time, regardless of the number of processors available.

Amdahl's law can be formulated as follows. For a given serial program let us denote by  $t_s$  the total execution time, by  $t_{ss}$  the execution time of the serial parts of the program which cannot be parallelized, and by  $t_{sp}$  the time spent on a single processor in executing the parallel portions of the programs. We have, therefore:

$$t_s = t_{ss} + t_{sp} \tag{2-3}$$

Let *s* be the ratio between  $t_{ss}$  and  $t_s$ :

$$s = \frac{t_{ss}}{t_s} \tag{2-4}$$

The parallel execution time on p processors is:

$$t_p = t_{ss} + \frac{t_{sp}}{p} \tag{2-5}$$

Consequently, the speedup becomes:

$$S = \frac{t_s}{t_p} = \frac{t_{ss} + t_{sp}}{t_{ss} + \frac{t_{sp}}{p}} = \frac{1}{s + \frac{1-s}{p}} \le \frac{1}{s}$$

(2-6)

This last equation expresses the fact that the speedup is limited by a limit which is independent of the number of processors and the structure of the machine. This result is known as Amdahl's

2

law [Amdahl67][Amdahl88]; later, this law was generalized by Lee [Lee80]. Since this formula does not take into account any reduction in speedup due to synchronization, it could even be considered as a favorable point of view of parallel processing.

Amdahl's law was used as a powerful argument against the use of parallel processors, especially systems with a large number of processing units. Since Amdahl's predicts that even with an infinite number of processors, a program with  $s \ge 0.005$  (which was considered as a realistic lower bound for *s*) would never achieve a speedup greater than 200. The argument points that it is may be a waste of money to develop (especially massively) parallel processing.

Several research groups (e.g. Sandia National Laboratories) have demonstrated that this last consideration is not valid. In fact, they observed speedups in excess of 1000 on several parallel programs. They achieve such a result by increasing considerably the amount of parallelizable work without increasing the sequential portion of the program, i.e. reducing s. These results do not invalidate Amdahl's law, but point out the importance of understanding the assumption of this law. A fundamental assumption in Amdahl's formula is that the percentage of time spend in executing the parallel sections of the code is independent of the number p of processors. In practice, this is not obvious, since it would amount of taking a fixed-size problem and running it on extremely large numbers of processors. Rather, the problem size tends to scale with the number of processors. If we are interested in developing a parallel application on a very large number of processors, the application is certainly also very large. When the size of a problem is scaled up, frequently the serial portion of the program does not increase proportionately to the problem size. For example, if a finer grid is used or the number of time steps is increased, the serial portion of the program is not affected, but the parallel portion increases [Leiss95]. In order to take into account these considerations, the Sandia National Laboratories developed the scaled speedup model [Gustafson88]. This model differs from Amdahl's law in that the serial execution time  $t_{ss}$  is considered as independent of the problem size and only the parallel portion scales up with the problem size.

In order to better understand the implication limits of the Amdahl's law, let us consider the following noncomputing problem taken from [Foster94]. Assume that 999 of 1000 workers on an express way construction project are idle while a single worker completes a sequential component of the project. We would not view this as an inherent attribute of the problem to be solved, but as a failure in management. For example, if the time required for a truck to bring material to a single point is a bottleneck, we could argue that the road should be under construction at several points simultaneously. Doing this would undoubtedly introduce some inefficiency - for example, some trucks would have to travel further to get to their point of work - but would allow the entire task to be finished more quickly. Similarly, it appears that almost all computational problems admit parallel solutions. The scalability of some solutions may be limited, the challenge is to find the optimal way to schedule the tasks in parallel. One must not build parallel applications by incrementally parallelizing sequential programs. Parallelism should be the central point that suggests the guiding lines of the algorithm. Finding optimal parallelization strategies is the main challenge.

Amdahl's law suggests how difficult it is to reach ideal speedup. Arranging schedules efficiently in parallel requires a large effort, similar to the management effort necessary to coordinate 1000 workers. This is the fundamental reasons why we believe that programming environments such as MPI do not provide an efficient framework for parallel processing. In such an environment, there is no concrete distinction between the serial work and parallel scheduling. It is like if in real life, there would be no difference between being a worker or a manager. The CAP language extension separates clearly the serial tasks, which are expressed in C++, and the flowgraph describing the parallel schedule. The flowgraph is described with dedicated CAP keywords and constructions. The language offers several parallel constructions and asynchronous execution models which can be combined together to form new parallel schedules. This way, the programmer can focus his attention on building efficient parallel schedule independently from the conception of serial routines.

#### 2.2. Granularity

This section poses the problem of how to make efficient use of parallel systems. Programming parallel systems requires that one starts with a study of the parallelism inherent in the problem to be solved. Thus, the question of where parallelism can occur arises. As pointed out by [Leiss95], several parallelization levels are possible:

- 1) At the job level

- 2) At the program, function or thread level

- 3) At the instruction level

- 4) At the arithmetic and bit level

These four levels are presented in increasing granularity order. The first level offers the lowest granularity, since there will typically be a few tasks at that level. At the opposite, the last level has a very high granularity. The question is to determine which levels are concerned by high performance parallel computing on cluster based parallel computers. Level one (job management) is rather uninteresting since independent tasks by definition can be executed in parallel. Operating systems or dedicated job management tools such as LSF [Xu01] handle the problem of assigning tasks (eventually dynamically) to processors, but it is not the main topic of high performance parallel computing. The fourth level (parallelization at the bit level) concerns the internal architecture of the processor and some compilers. This level is not relevant for the programmer of parallel applications. The programmer is concerned by levels two and three, i.e. instruction parallelism and thread or function level parallelism.

Instruction level parallelism requires *fine* granularity. Because of the fine granularity, this level of parallelization is mostly used on *vector* computers. Generally, the programmer does not express explicitly the parallelism. Instead, the programmer develops a sequential program (usually in Fortran or C). The application is parallelized by applying a *vectorizer* to the sequential program [Leiss95]. Important in this process is that in doing this translation from sequential to

vector code, the compiler uses only syntactic properties of the program; in other words, there is no need for any understanding of the meaning of the program in order to do the vectorization. In contrast to initial expectations, several scientific and engineering applications have proved to be amenable to automatic vectorization. Furthermore, this approach benefits from the advantage that the programming effort necessary to vectorize the code is in general very low. Nevertheless, this approach requires the use of a specific expensive hardware, and is not well suited for I/O intensive or interactive applications. In addition, from the theoretical point of view, automatic vectorization is unlikely to adhere to any modular design approach. These reasons limits the usage of vectorized applications.

An automatic parallelization tool will never be able to transform a sequential QuickSort into a more appropriated parallel MergeSort. Such a transformation requires the understanding of the meaning of the program which could not be deduced from the syntactic properties of the sequential program. Let us now discuss the second level of parallelization grain, the function or thread based parallelization, which requires *coarse* grain. At this level, the programmer fomulates explicitly the expression of parallelism and focuses his attention on developing an efficient parallel schedule. The CAP language extension is based on these considerations and helps the programmer in its task. CAP facilitates the programmer's work by offering several high-level parallel constructions avoiding the implementation of low-level routines necessary to the execution of the parallel schedules. The high-level of abstraction offered by the CAP framework lets the developer focus his attention on the management of parallel schedules.

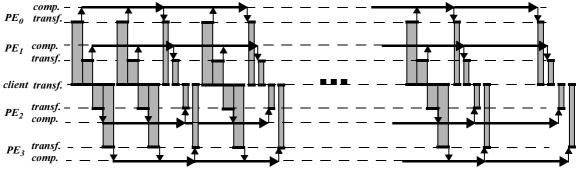

#### 2.3. Parallel processing and pipelining<sup>1</sup>

In this section we introduce two fundamental ways of executing tasks in parallel. We distinguish *pipelining* and parallel processing. In order to explain clearly the differences between these two parallelization techniques, let us take an example from real life. Anyone who has done a lot of laundry has intuitively used pipelining or parallel processing. Let us study the several ways to accomplish this task [Patterson97].

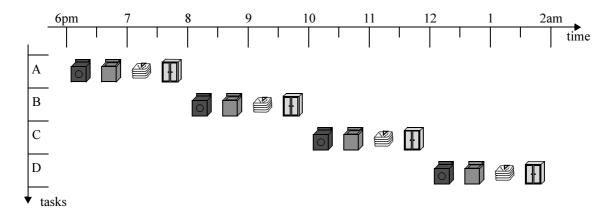

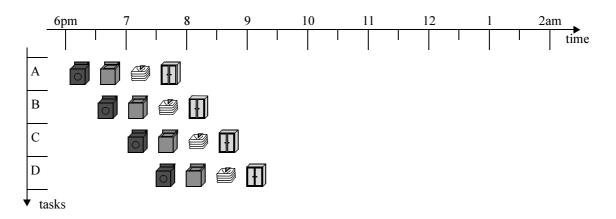

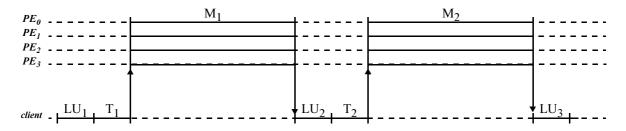

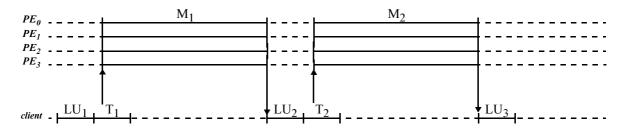

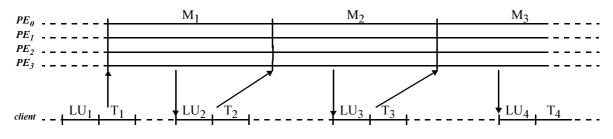

The serial approach to laundry would be: (1) Place on dirty load of clothes in the washer, (2) when the washer is finished, place the wet load in the dryer, (3) when the dryer is finished, place the dry load on a table and fold, (4) when folding is finished, put the clothes in the ward-robe. When the clothes are put away, then the next dirty load starts over, and the whole process is repeated. For this example, we suppose that each step of the task takes 30 minutes and that we need to repeat the task four time (tasks A, B, C, D). Figure 2.1 suggests that if the first load is placed in the washer at 6 pm, the last task terminates at 2 am.

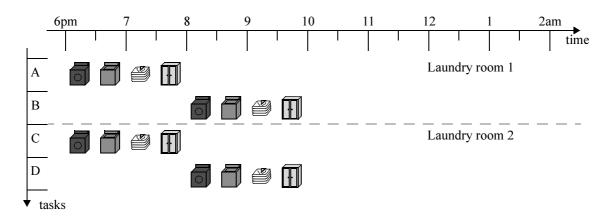

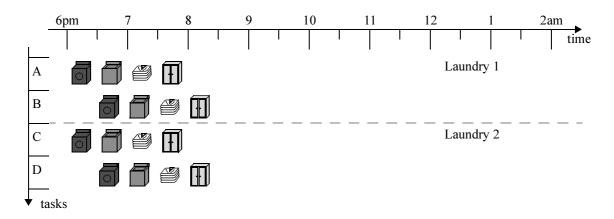

If two laundry rooms are available, the process can be improved by using in parallel both laundry rooms. Figure 2.2 illustrates this process. The tasks A and C start both at 6 pm. At 8 pm the

<sup>&</sup>lt;sup>1</sup> Pipelining refers in general to the internal architectures of processors. In the thesis, we use this terminology in a more general sense.

tasks B and D start and they terminate at 10 pm. By working in parallel with both laundry rooms the eight hours serial work is reduced to four hours.

Fig. 2.1 Doing the laundry sequentially

Fig. 2.2 Doing the laundry in parallel

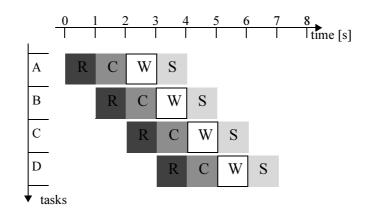

Fig. 2.3 Doing the laundry in pipeline

If only one laundry room is available, doing the laundry in pipeline takes less time than the sequential approach. The pipelined approach is presented by Figure 2.3. As soon as the washer is finished with the first load and placed in the dryer, the washer is loaded with the second dirty load. When the first load is dry, it is placed on the table and the folding starts, at the same time, the wet load is moved to the dryer, and the next dirty load into the washer. Next, the first load A is placed in the wardrobe, the second load B is folded, the dryer receives the third load, and the fourth load D is moved into the washer. At this point (7h30 pm), all steps - called *stages* in pipelining - are operating concurrently. The pipeline reaches the *steady state*. The time until the pipeline reaches the steady state is called the pipeline *starting cost*. Similarly, the pipeline has also an *ending cost*. As long as separate resources are available for each stage, the task can be pipelined.

The pipelining paradox is that the time from placing a single dirty sock in the washer until it is dried, folded, and put away is not shorter for pipelining; the reason pipelining is faster for many loads is that everything is working in parallel, so more work is achieved per hour. If all the stages take about the same amount of time and there is enough work to do, then the speedup due to pipelining is equal to the number of stages in the pipeline. [Patterson97].

Fig. 2.4 Doing he laundry in a parallel-pipeline fashion

The final improvement consists of combining both parallelization techniques. If two laundry rooms are available, it is possible to accomplish the task in a parallel-pipeline fashion. Figure 2.4 illustrates this process. In this figure the pipeline never reach the steady state (there is no time where all pipeline stages are working in parallel) because there are not enough tasks to perform.

The previous considerations can be transposed to parallel computing. Parallel processing consists obviously of running the algorithm using several processors, just as using two laundry rooms (Fig. 2.2). Pipelining seems to be more difficult to transpose. One possible way to achieve pipelining is to consider that generally an algorithm is composed of computing and I/O. By I/O we mean mostly disk accesses and network transfers. Modern technologies allow the hardware responsible for I/O to have a Direct Memory Access (DMA), i.e. disk or network accesses can be performed without loading significantly the processor. Therefore, it is possible to pipeline I/O and computing. If the application is compute-bound, by performing the I/O and computation in pipeline it's possible to *hide* the I/O time. Similarly, if the application is I/O-bound, an efficient pipeline allows to hide the computation time. If a parallel algorithm performs it's I/O serially (as it is commonly), it will consequently fall under the Amdahl's law. By pipelining the I/O and the computation the parallel algorithm can be improved.

Fig. 2.5 Executing the encryption program in pipeline (1 MB blocks)

Let us give a concrete program example, where parallel-pipeline processing is well suited. The program consists of reading a 4MB file from a hard disk, performing some computation to encrypt it, writing the encrypted file (also 4MB) back to a second hard disk and sending the encrypted file over the network. By stripping the file in four blocks of 1MB it is possible to perform the computation in a pipelined fashion. Figure 2.5 illustrates this process. Each task (A, B, C or D) consists of reading 1MB from the disk (R), encrypting it (C), writing it back to a second hard drive (W) and finally sending it over the network (S). We suppose that each step takes the same amount of time (1 second). Each task is working on a different part of the file: task A on the first MB, task B on the second MB, task C on the third MB and task D on the last MB. The pipeline stages (R, C, W and S) can be performed in parallel since they use different resources. The last figure can be compared with Figure 2.3. If several computers are available the encryption program can be improved by implementing a parallel-pipeline execution model like in Figure 2.4.

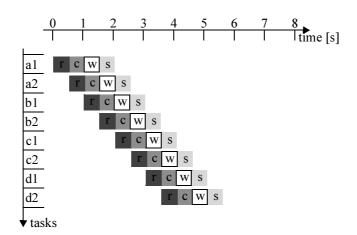

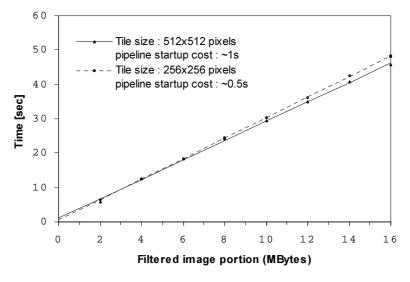

Another approach to improve the pipelined encryption program of Figure 2.5 is described by Figure 2.6. Instead of splitting the file into 1MB blocks, we use 0.5MB blocks. Each step of the pipeline takes now 0.5 second instead of 1 second. Since the tasks are smaller there are more tasks to perform. The new version of the encryption program is composed with 8 tasks: a1, a2, b1, b2, c1, c2, d1, d2. Reducing the task size increases the number of tasks (finer grain), reduces the pipeline starting and ending cost, and therefore improve the program execution time. The 1MB block size program takes 7 second to terminates against 5.5 second for the 0.5MB block size encryption program. This indicates - from the pipelining point of view - that the task should be as small as possible. This consideration must be balanced with the fact that smaller tasks have

a relative higher latency. For example, when a disk read access of 100MB is made the latency can be ignored. But when a 1B access is made the latency becomes dominant against the throughput. From the latency point of view, it is more efficient to handle larger tasks. The ideal strategy is a compromise in between taking into account pipelining and latency.

Fig. 2.6 Executing the encryption program in pipeline (0.5 MB blocks)

Parallel and pipeline execution model are critical issues in terms of parallel processing. The CAP language extension allows the programmer to specify parallel and pipeline constructions, and to combine them together to formulate more complex execution schedules. Let us ignore for now the syntax of the CAP language extension. Conceptually the CAP programmer is able to formulate the execution schedule of Figure 2.4 by specifying something like:

Parallel( Pipeline(A,B) , Pipeline(C,D) )

Clearly the programmers do not care about any synchronizations between the several pipeline stages and between the different tasks. The programmer formulates at a high-level of abstraction the parallel execution schedule. The CAP kernel is responsible for deducing the dependencies and for managing the required synchronizations. Inside the CAP kernel, everything is performed in an asynchronous manner allowing parallel-pipeline executions. From the CAP programmer point of view, the CAP kernel could be considered as a parallel scheduler. The possibility to formulate at a high-level of abstraction complex parallel-pipeline execution schedules is one of the main issues of the CAP language extension.

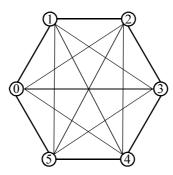

#### 2.4. Master-slave or distributed system

There are two fundamental ways of organizing parallel schedules: in a *master-slave* or in a *distributed* fashion. By a distributed system we mean that each processing node, part of the parallel system, is responsible (1) for performing some computation and (2) for cooperating with the other processing node. Cooperating means exchanging some information with other processing nodes. The results of this communication can induce several modifications in the current or further computation activities. Within a parallel algorithm organized in a distributed

fashion, each processing node exchanges information with all or at least with some neighboring processing nodes. Implementing distributed systems can be difficult, since each processing node must take into account the activities of other nodes.

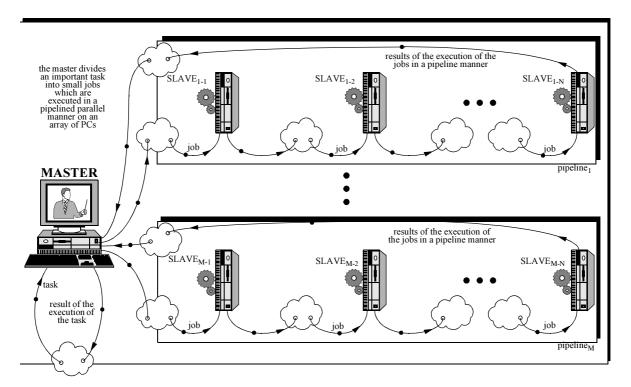

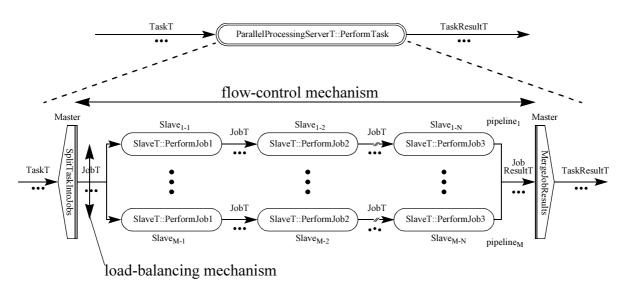

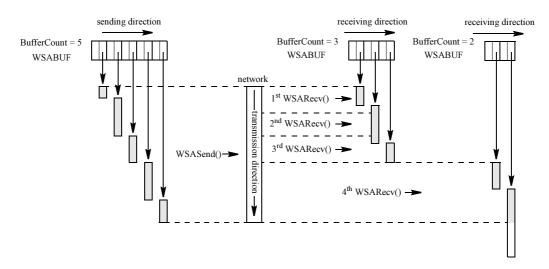

In general, implementing a master-slave parallelization scheme requires less programming efforts. In a master-slave scheme, the slaves are responsible to perform some computation, but the slaves do not communicate with each other. They perform their tasks independently. Instead a master is responsible to coordinate the slaves. This coordination is ensured by several information exchanges between the master and the slaves. The master can be considered as the manager of a team of workers. In a master-slave scheme, the coordination effort is localized at a single place, the master. This explains why implementing a master-slave scheme is simpler than a distributed system. Nevertheless, it's not always possible or efficient to parallelize a program in a master-slave manner.

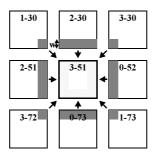

There is no exact border between the master-slave and distributed parallelization models. Several execution schedules can be categorized in neither of the two execution schemes. For example, let us consider the problem of image filtering (Chapter 7). Such a problem can be parallelized by letting a master divide the input image into tiles. The master then distributes the tiles to the slaves. The slaves filter the tiles received from the master and send the filtered tiles back to master. Once the master has collected all the filtered tiles, the program is terminated. The slaves, in order to perform the filtering step, need to receive some data from the neighboring tiles located on other slaves. Thus the slaves need to exchange information between themselves, like in a distributed system.

The master-slave parallel organization scheme has been criticized by the scientific community. The major argument against the master-slave scheme is that it is not scalable. In fact, the number of slaves cannot increase infinitely, because the master becomes a bottleneck. This argument is clearly true, but we want to formulate three comments on this consideration. First, Amdahl's law suggests that the problem of scalability is not specific to the master-slave scheme, but inherent to any parallelization model. Second, the master-slave scheme could be, if necessary, extended hierarchically, by introducing masters of masters. The hierarchical organization of our society seems to indicate that such a system works pretty well. Finally, the question of knowing if a system is infinitely scalable is not always relevant. Rather, the problem is to perform parallel processing in order to achieve a finite and specified speedup. The corresponding question is to choose the appropriate parallelization scheme (e.g. requiring the least programming effort).

The CAP language allows the programmer to specify either master-slave or distributed parallelization schedules. Nevertheless, CAP facilitates the development of master-slave schedules. This result comes from the fact that we are mostly interested in high-performance parallel computation on a limited number of nodes, e.g. 50. On such a number of processing nodes, masterslave schedules are generally efficient.

#### 2.5. Load balancing

Imperfect partitioning may have a dramatic impact on the overall performance of a parallel program. Suppose a program that takes 1000 seconds on a single processor can be partitioned into 100 task that can be executed without incurring overhead or waiting because of dependences. With a perfect partition, each task would take exactly 10 seconds. However, suppose that all tasks except one take 9.9 seconds and that the remaining task takes 19.9 seconds. If the 100 tasks are distributed among 2 processors, each processor executing 50 tasks, the system achieves a speedup of:

$$S = \frac{1000}{49 \times 9.9 + 19.9} = 1.98 \tag{2-7}$$

If we decide to distribute the 100 tasks over 100 processors the speedup becomes:

$$S = \frac{1000}{19.9} = 50.25 \tag{2-8}$$

As we see, a difference of 10 seconds between tasks, which is small compared to the 1000 seconds required to accomplish the work sequentially, becomes critical when increasing the number of processors.

A critical issue of parallel algorithms is to balance the load between the contributing processors, i.e. achieving *load balancing*. We distinguish *static* load balancing and *dynamic* load balancing. Static load balancing consists of assigning statically some work to processors. Unfortunately, static partitioning of several algorithms yields poor performance because of substantial variation in the execution time of each partition. Dynamic load balancing is more elaborated, it consists of distributing the load at run time. When a processor runs out of work, it should get more work from another processor. Dynamic load balancing is more flexible and achieves better performance than static load balancing.

Load balancing is another important feature of the CAP language extensions. CAP allows the programmer to specify, at a high-level of abstraction, static or dynamic load balancing directives. The CAP kernel interprets these directives and balances the load of the specified tasks among the different processors.

#### 2.6. Asynchronous behaviour

Asynchronous behavior is opposed to synchronous execution. In a synchronous execution mode all the processors receive computation work at specific time. This may result in some inefficiencies, letting several processors idle. An improvement consists of letting each processor work independently from the others. Instead of receiving tasks synchronously, each processor takes its work from a task-stack. Such an asynchronous execution mode enables each processor to work at its own speed.

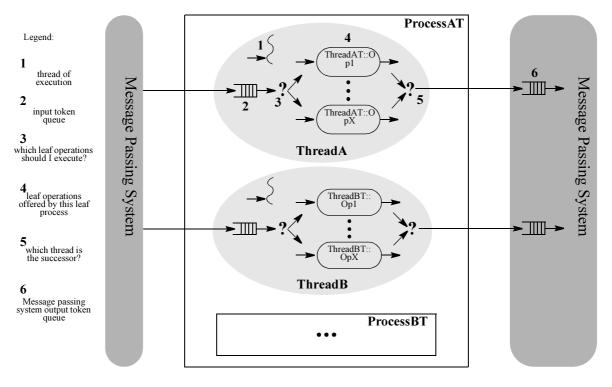

The CAP execution model is based on asynchronous behavior. The CAP kernel associates to each thread composing the parallel application a queue. This queue is filled with tasks (produced by other tasks). As soon as a thread terminates a task, it takes a new task from its queue independently from the other threads. The asynchronous behavior of the CAP kernel is hidden to the programmer. The CAP program describes how the tasks are scheduled. The CAP kernel acts at a lower level using asynchronous routines to realize the desired schedule.

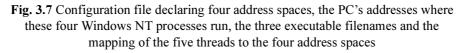

#### 2.7. Flexibility

Another important issue of the CAP framework is to allow the programmer to deal with logical processes. Instead of developing architecture dependent programs, the developer programs at a logical level. Within the CAP framework the programmer declares logical processes and develops parallel schedules using these logical processes. At execution time, the logical processes are mapped to OS processes. The mapping is defined by a configuration file. The configuration file name (and path) is given on the command line arguments at execution time. The dissociation of OS processes and logical processes induces some flexibility. The same program can run, without re-compilation, with different numbers of contributing processors. It can also take into account the usage of heterogeneous hardware, like single-processor or bi-processor computers. The developer can at execution time customize the configuration file to adapt and take advantage of the hardware specificities of the cluster on which the program should run.

#### 2.8. Reliability and error handling

When thinking about parallel systems, one must be concerned by reliability. If we run our parallel application on a cluster of 100 PCs, the probability of failure is 100 times the failure probability of a single component. If no adequate error handling exists, the failure of a single component of the cluster can crash the whole parallel application. To avoid such a situation, an effort must be invested for handling errors. Error handling is not costless. Reliability is, in a way, opposed to high-performance computing. The question is not how to built a reliable system, but how to build a reliable system that consumes as less resources as possible for handling errors.

Letting a parallelization tool featuring the ability of recovering from many kinds of errors induces indubitably a considerable error management overhead. A solution consists of letting the parallel program handle failures by implementing a *checkpoint and restart* paradigm [Gray92]. Within the checkpoint and restart paradigm, the application is responsible for saving (on one or several permanent storage devices) its status periodically (checkpoint). This strategy reduces the costs, since the application could decide when it is the most appropriated time to make a checkpoint. When a failure is detected, the parallel application is destroyed and restarted. When the application is restarted, it uses the information saved during the last checkpoint to recover. Using this strategy, only the computation time from the last checkpoint to the system crash is lost.

Within the development of the CAP framework, we have developed a tool which enables the capability of detecting a failure during the execution of a parallel application. Such a tool is commonly called a *watchdog*. If the watchdog detects a failure, it kills the parallel application and eventually reboots the whole system. Then the application is launched again. The application is responsible for using the information from the last checkpoint to recover from the failure.

#### 2.9. Summary

In this chapter we showed that building parallel algorithm cannot be considered as an extension of sequential algorithms. Efficient parallel solutions differ from serial solutions. Parallel scheduling is difficult and requires ingenuity, as suggested by Amdahl's law. We presented several commonly used techniques to improve parallel algorithms, such as pipelining, load balancing, and asynchronous execution behavior. We introduced the CAP language extension from the conceptual point of view. The several aspects discussed in this chapter are the fundamentals (building blocs) of CAP. Explaining the fundamentals of the CAP language extension from the conceptual point of view, rather than from the syntactical point of view, aims at helping the reader to better understand our motivation and philosophy.

# 3

# The CAP Computer-Aided Parallelization Tool

This chapter describes the CAP Computer-Aided Parallelization tool. The CAP language is a general-purpose parallel extension of C++ enabling application programmers to create separately the serial program parts and express the parallel behavior of the program at a high-level of abstraction. This high-level parallel CAP program description specifies a parallel schedule, i.e. a flow of data and parameters between operations running on the same or on different processors. CAP is designed to implement highly pipelined-parallel programs that are short and efficient. With a configuration map, specifying the layout of threads onto different PCs, these pipelined-parallel programs can be executed on distributed memory PCs. In this chapter, we concentrate on the technical aspects of the CAP framework.

## 3.1. Introduction

This chapter is intended to give readers the necessary background on the CAP methodology and programming skills required to understand the remainder of this dissertation. Most of the current chapter has been taken from [Messerli99a]. Readers who want to have a more in-depth view of CAP can read its reference manual [Gennart98a].

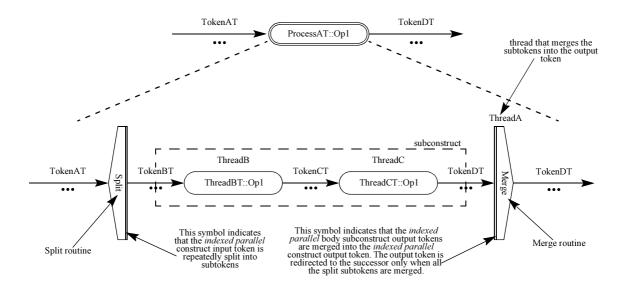

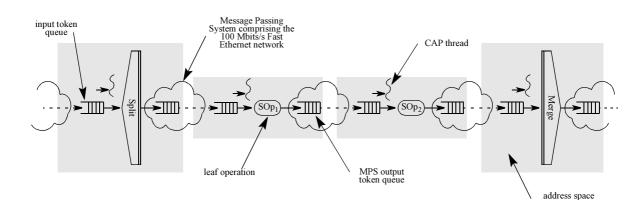

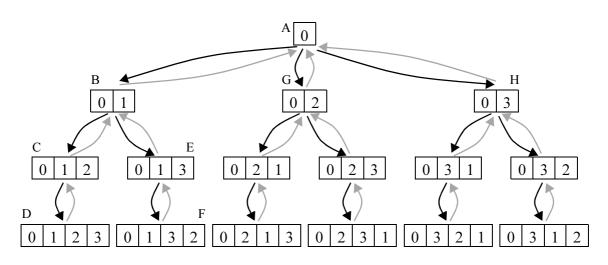

The CAP specification of a parallel program is described in a simple formal language, an extension of C++. This specification is translated into a C++ source program, which, after compilation, runs on multiple processors according to a configuration map specifying the mapping of the threads running the operations onto the set of available processors. The macro-dataflow model which underlies the CAP approach has also been used successfully by the creators of the MENTAT parallel programming language [Grimshaw93a][Grimshaw93b].

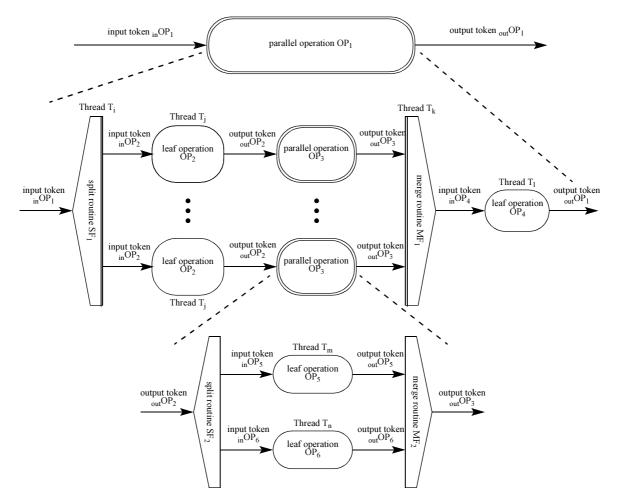

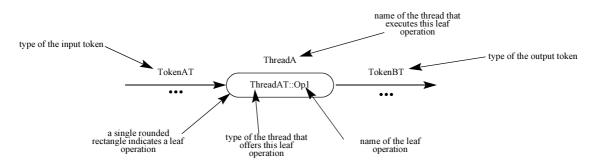

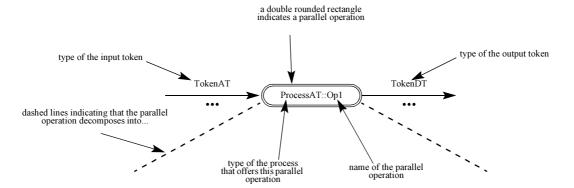

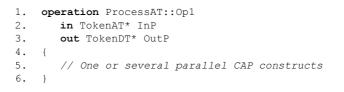

The control mechanism that selects for execution the primitive units of computation, i.e. sequential operations, is based in CAP on the macro-dataflow MDF model [Grimshaw93a] inspired by the dataflow computational model [Agerwala82][Denning86][Srini86][Veen86]. The CAP macro-dataflow computational model is a coarse grain, *data-driven* model and differs from traditional dataflow in four ways. First, the computation granularity is larger than in traditional dataflow. The basic units of computation are high-level tasks such as multiplying two matrices specified in a high-level language (C/C++ leaf operation in the CAP terminology), not primitive operations such as addition. Second, some operations may maintain state between invocations, i.e. have side-effects such as modifying shared global variables. Third, operations may only depend on the result of their single previous operation, i.e. single data dependency. Finally, in order to be able to have parallel executions of tasks, CAP has introduced two particular operations called *split* and *merge*. A split routine takes as input the token (CAP data structure, see Section 3.2) of its previous operation, and splits it into several sub-tokens sent in a pipelined parallel manner to the next operations. A merge routine collects the results and acts

as a synchronization means terminating its execution and passing its token to the next operation after the arrival of all sub-results.

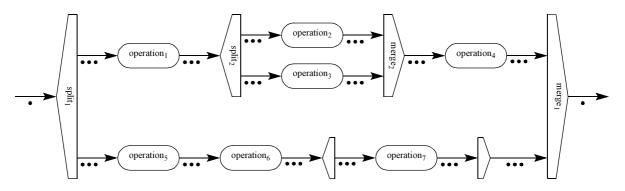

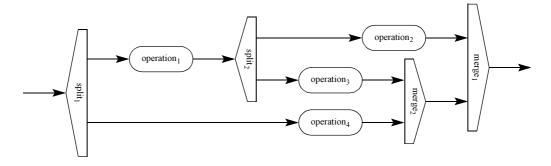

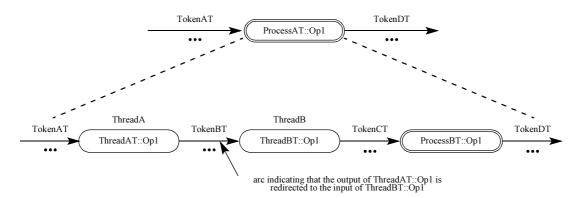

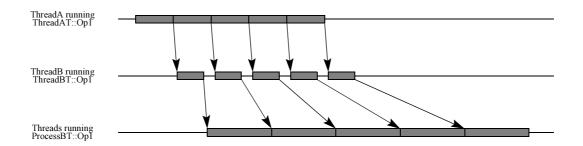

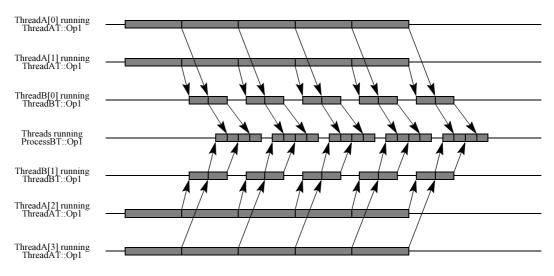

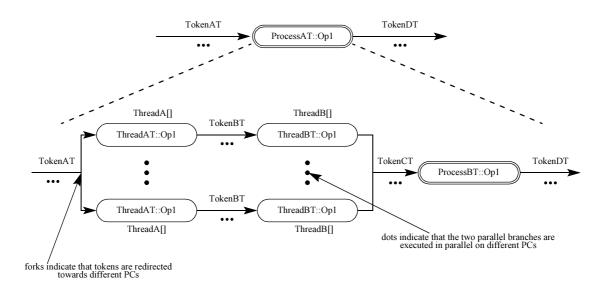

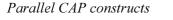

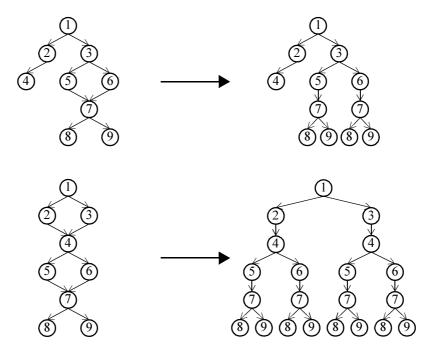

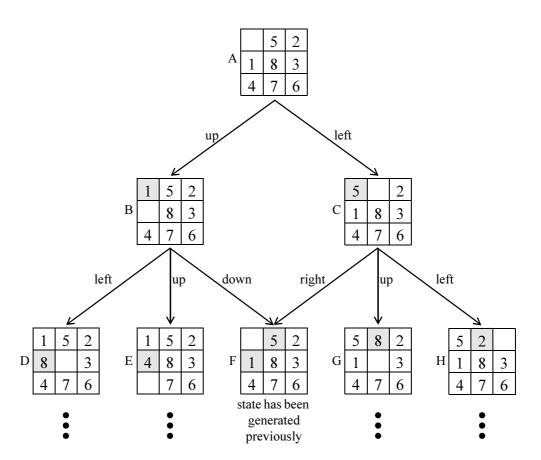

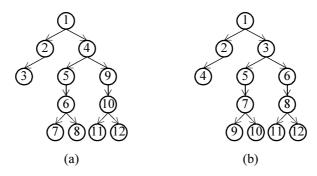

An algorithm is described in CAP by its macro-dataflow and graphically depicted by a *Directed Acyclic Graph* (DAG). DAGs are completely general, meaning that they can describe any sort of algorithm. Furthermore, they ensure that the generated code will be deadlock free. The CAP language extension enables the programmer to specify DAGs. Figure 3.1 presents a symmetric DAG, i.e. where all the split and merge points in the graph match pairwise. A recent extension to CAP enables the programmer to specify asymmetric DAGs as well, i.e. where split and merge points in the graph do not match pairwise (Fig. 3.2).

Fig. 3.1 An example of a CAP macro-dataflow depicted by a symmetric directed acyclic graph. Arcs model data dependencies between operations. Tokens carry data along these arcs. Split routines split input tokens into several sub-tokens sent in a pipelined parallel manner. Merge routines merge input tokens into one output token thus acting as synchronization points

Fig. 3.2 An asymmetric directed acyclic graph that can be described with the recent extension to CAP

Regarding communications, the CAP language does not explicitly provide synchronization tools such as semaphores, barriers, etc. A CAP program is self-synchronized by the data merging operations. Merge routines act as synchronization points returning their output tokens only when all the sub-tokens have been merged. The CAP computer-aided parallelization tool enables application programmers to specify at a high level of abstraction the set of threads which are present in the application, the processing operations offered by these threads, and the flow of data and parameters between operations. This schedule specification completely defines how operations running on the same or on different PCs are sequenced, and what data and parameters each operation receives as input values and produces as output values.

The term high-level is used to emphasize the fact that the CAP computational model works at a high-level of abstraction compared with other parallel imperative languages such as High-Performance Fortran [Loveman93], Multilisp [Halstead85], Concurrent Pascal [Hansen75], Occam [Miller88][Galletly96][Inmos85] and compared with other parallel programming environments such as Express [Parasoft90], PVM [Beguelin90][Sunderam90], Linda [Carriero89a] [Carriero89b] and MPI [MPI94].

The CAP methodology consists of dividing a complex operation into several suboperations with data dependencies, and to assign each of the suboperations to a thread in the thread hierarchy. The CAP programmer specifies in CAP the data dependencies between the suboperations, and assigns explicitly each suboperation to a thread. The CAP C/C++ preprocessor automatically generates parallel code that implements the required synchronizations and communications to satisfy the data dependencies specified by the user. CAP also handles for a large part memory management and communication protocols, freeing the programmer from low level issues.

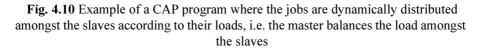

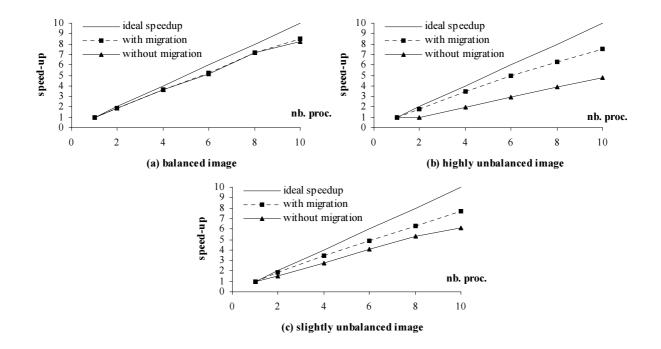

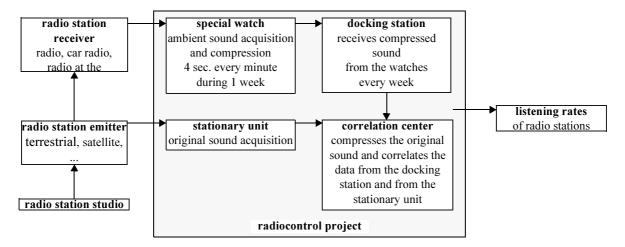

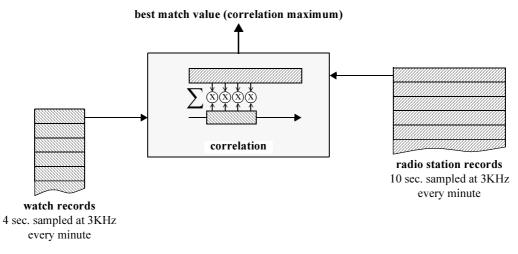

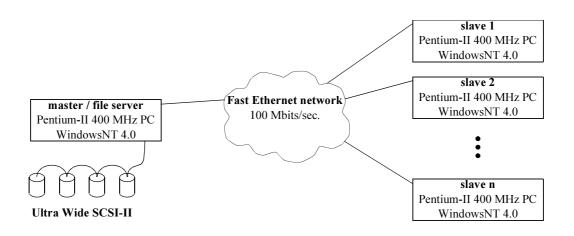

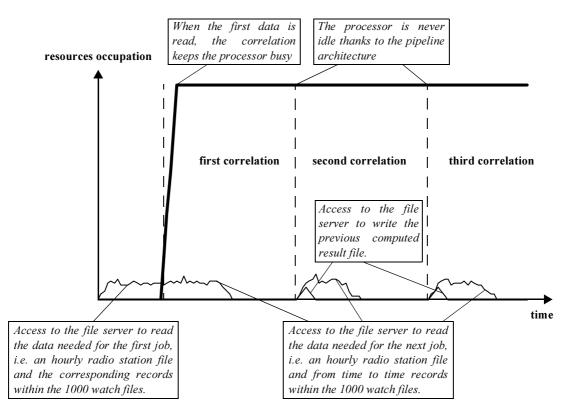

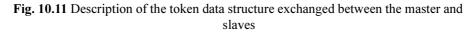

CAP operations are defined by a single input, a single output, and the computation that generates the output from the input. Input and output of operations are called *tokens* and are defined as C++ classes with serialization routines that enable the tokens to be packed or serialized, transferred across the network, and unpacked or deserialized. Communication occurs only when the output token of an operation is transferred to the input of another operation. The CAP's runtime system ensures that tokens are transferred from one address space to another in a completely asynchronous manner (socket-based communication over TCP/IP). This ensures that communication takes place at the same time as computation<sup>1</sup>.